Samsung Electronics segna un nuovo traguardo. La società sudcoreana ha annunciato di aver cominciato la produzione di massa di chip frutto di processo costruttivo a 3 nanometri (nm), ovvero la tecnologia produttiva più avanzata nel campo dei semiconduttori. La corsa alla miniaturizzazione consente di ridurre i consumi energetici e lo spazio occupato, migliorando al contempo le prestazioni di calcolo, e questo è noto, ma è interessante capire come si arrivi a questo risultato.

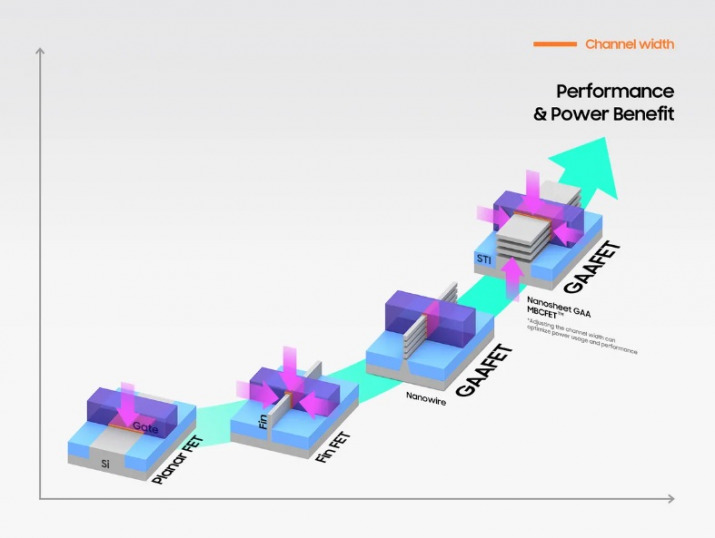

Più precisamente, rispetto ai chip a 5 nanometri della stessa Samsung, quelli a 3 nm riducono del 45% il dispendio energetico, occupano il 16% di spazio in meno ed elevano del 23% le performance. Samsung è riuscita a ottenere questo risultato grazie a una nuova architettura transistor Gate-All-Around (GAA) proprietaria, chiamata Multi-Bridge-Channel FET (MbcFET).

Questa tecnologia non presenta le limitazioni dei componenti FinFET, potendo ridurre il voltaggio richiesto dal processore e aumentando la capacità del drive. L’uso di tutti e quattro i lati dei canali permette un migliore passaggio di corrente tra i gate che circondano i canali stessi.

(Immagine: Samsung; nella foto in alto: Michael Jeong, corporate vice president, Ja-Hum Ku, corporate Evp, e Sang Bom Kang, corporate Vp della divisione Samsung Foundry Business, reggono wafer da 3nm nel campus Samsung di Hwaseong)

La prima applicazione prevista per questi nuovi prodotti sono i processori destinati ad applicazioni che richiedono alte prestazioni e bassi consumi energetici. In un secondo momento saranno estesi anche ai processori per smartphone. Samsung ha sottolineato di voler continuare a lavorare in ottica di ecosistema, per consentire la massima adattabilità rispetto alle tecnologie di destinazione. L’azienda non ha specificato quale sia il cliente per cui la produzione di massa è stata avviata, ma nell’annuncio vengono rimarcate le collaborazioni con Ansys, Cadence, Siemens e Synopsys.